美国科研团队制造出首枚单片式3D芯片,这款芯片的独特架构有望开启人工智能硬件与本土半导体创新的新纪元。在硬件测试与仿真实验中,这款3D芯片的性能比传统2D芯片高出约一个数量级。不同于当前主流的平面2D芯片,这款新型原型芯片的关键超薄组件如同高楼大厦般垂直堆叠,其纵向布线如同高速电梯般实现海量数据的快速传输。

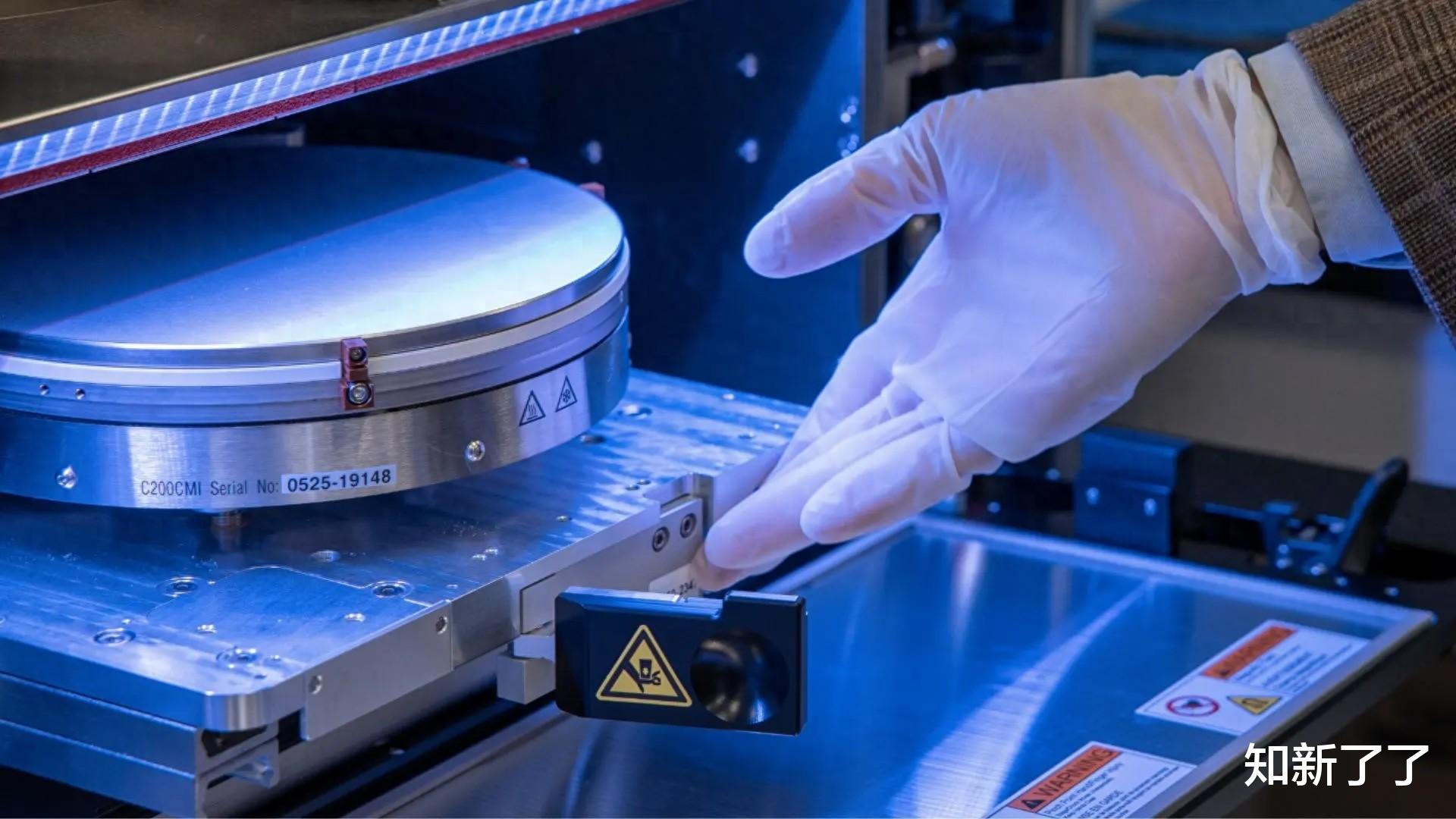

该芯片创纪录的垂直连接密度,以及存储单元与计算单元的精妙交织设计,突破了长期制约平面芯片发展的性能瓶颈。斯坦福大学电子工程学教授苏巴希什·米特拉表示:"这开启了芯片生产与创新的全新时代。此类技术突破将帮助未来AI系统实现千倍的硬件性能飞跃。"虽然学术界此前已制造出实验性3D芯片,但这是首款在商业代工厂生产且展现显著性能优势的3D芯片。

研究团队指出,传统2D芯片的组件布局在单一平面上,内存有限且分散,数据只能通过少量漫长而拥挤的路径传输。由于计算单元运行速度远超数据传输速度,加之芯片无法在近端存储足够内存,系统始终处于等待数据的状态。这种被称为"内存墙"的瓶颈,正是指芯片的数据供给能力无法匹配处理速度的困境。

卡内基梅隆大学助理教授塔塔加塔·斯里马尼解释道:"通过纵向集成存储与计算单元,我们能以更快的速度传输更多信息,就像摩天大楼的电梯群能同时运送大量乘客往返不同楼层。"这项研究由斯坦福大学、卡内基梅隆大学、宾夕法尼亚大学、麻省理工学院的工程师与SkyWater Technology公司合作完成。

早期硬件测试显示,该原型芯片性能已达同类2D芯片的四倍。对具有更多堆叠层的未来版本进行的仿真实验表明,其性能还将实现更大飞跃。根据研究数据,在包括源自Meta开源LLaMA模型的实际AI工作负载测试中,增加堆叠层数的设计方案可提升高达十二倍的性能。

研究团队宣称,该设计为"能耗延迟积"这项平衡速度与能效的关键指标带来了百倍至千倍的改进空间。通过大幅缩短数据传输距离并增加垂直通道,芯片既能实现更高吞吐量,又能降低单次运算能耗——这种组合曾被普遍认为传统平面架构无法企及。

宾夕法尼亚大学助理教授罗伯特·M·拉德韦指出:"内存墙与微型化壁垒形成了致命组合。我们通过紧密集成存储与逻辑单元,并以极高密度向上构建的方式正面攻克了这个难题。这就像曼哈顿的立体城市规划——我们能在有限空间容纳更多功能单元。"

如果朋友们喜欢,敬请关注“知新了了”!