杜克大学的工程师们展示了借助一种常见的器件架构来测试二维器件的方法。此架构会引发一种名为“接触栅控(contact gating)”的现象,进而使得性能前景被夸大,幅度高达六倍之多。

近二十年来,二维半导体始终被视作硅晶体管的补充者,甚至是潜在的继任者,它有望助力实现体积更小、运行更快且能耗更低的处理器。为了简化生产以及测试流程,该领域的众多研究皆采用一种会引发“接触栅控”现象的架构,以此来评估二维半导体的潜力。

杜克大学电气工程师的最新研究发现表明,这种方法仅在理论层面夸大了这些晶体管的性能,实际上并不能转化为商业技术。

这项名为《利用对称双栅结构研究接触栅控对单层二维晶体管微缩的影响》(Impact of Contact Gating on Scaling of Monolayer 2D Transistors Using a Symmetric Dual - Gate Structure)的研究,于2026年2月17日在线发表于《ACS Nano》期刊,其出自Aaron Franklin教授的实验室。

深度报道内容中,Franklin表示:“大多数有关高性能二维晶体管的报告,采用的都是一种与商业技术并不兼容的器件设计。”他进一步指出,“我们所揭示的是,这种设计改变了晶体管的工作模式,进而显著夸大了其性能。若不考虑这一因素,便难以公正地评估这些材料在未来晶体管技术中的表现。”

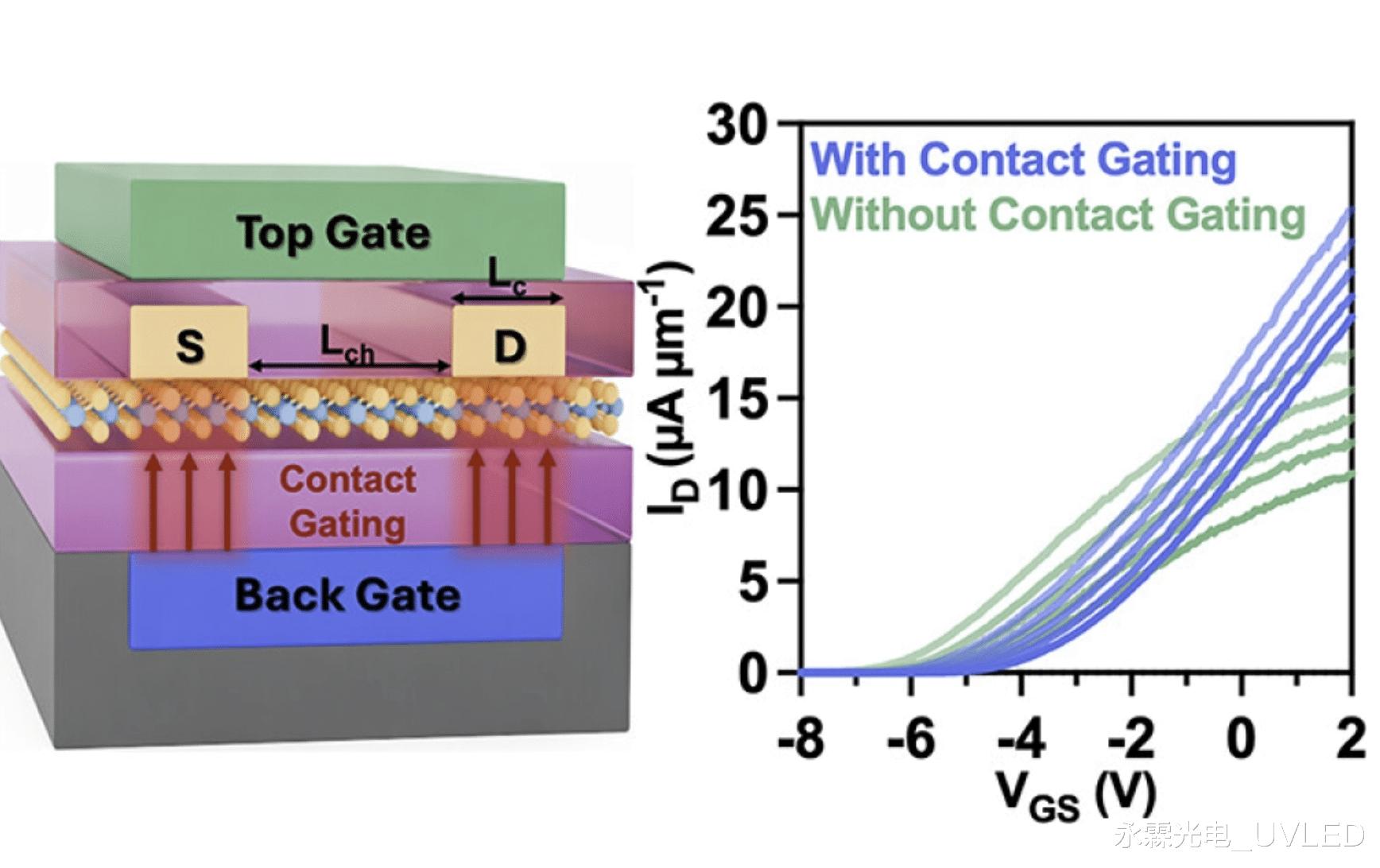

为探究二维材料的性能,研究人员通常会借助简单的“背栅(back - gated)”架构。该架构将所有晶体管组件构建于一块硅片之上,旨在简化制造流程并便于开展快速实验。在此设置下,一层超薄的二维半导体(例如二硫化钼MoS₂)处于两个金属接触电极之间,电流由此半导体通过。通过将硅衬底用作栅极控制,便可实现电流流动的开启或关闭。

然而,栅极的作用并非仅仅调节二维半导体沟道;在“背栅”架构里,它还会对半导体下方的金属接触部分产生影响。这便引发了一种名为“接触栅控”的现象——一种通过栅极降低接触电阻来增强晶体管性能的效应。

Franklin称:“增强性能看似是件好事。但尽管这种架构十分适合实验室的基础测试,它却存在速度和漏电流等物理局限,无法应用于实际的器件技术。”

为揭示这一潜藏于数百项二维晶体管实验室研究中的影响因素,Franklin实验室的博士生Victoria Ravel耗费一年时间研制出一种新型器件架构,使团队得以直接测量接触栅控对性能的改变程度。她构建了一个对称双栅晶体管,其中包含位于同一二维半导体沟道、接触和材料上方及下方的栅极。控制器件使用背栅或顶栅的唯一差异在于是否存在接触栅控,因而她能够进行一对一的比较。

Ravel表示:“在制造过程中,你永远无法预知会遭遇何种状况。当以如此微小的尺寸进行制造时,在物理极限范围内开展工作变得异常艰难。”

结果令人惊愕。在较大的器件中,接触栅控使性能大约提升了一倍。当Ravel将器件缩小至与未来技术相关的微小尺寸时,接触栅控效应愈发显著。在沟道长度为50纳米、接触长度为30纳米的情况下,接触栅控使性能提升幅度高达6倍。

Franklin解释道,随着器件尺寸的缩小,接触电阻在整体性能中占据主导地位。任何改变接触行为的机制都变得愈发关键。鉴于多年来多数二维晶体管报告结果均采用背栅架构,Franklin和Ravel的发现具有广泛的影响力。

接下来,该团队计划进一步推进微缩工作,将接触长度缩小至15纳米,并研究替代的接触金属以降低接触电阻。更为广泛的目标是为将二维半导体集成到未来的晶体管技术中确立更为清晰的设计规则。Franklin表示:“倘若二维材料有朝一日要取代硅沟道,我们需要诚实地面对器件架构如何塑造我们的测量结果。这项工作正是为了奠定这一基础。”

永霖光电-UVSIS-UVLED紫外线应用专家-独家发布