MOS驱动功率指驱动芯片为MOSFET栅极充放电所消耗的电能,直接影响系统效率、发热和可靠性。它并非单一数值,而是由静态功耗、动态功耗和导通损耗三部分构成,需根据开关频率、栅极电荷和驱动电压精准计算与优化。

一、驱动功率的核心来源

MOS驱动功率主要由以下三部分构成:

1. 静态功耗(Static Power)由驱动芯片内部电路的漏电流引起,包括偏置电路和逻辑单元的待机电流。现代驱动芯片通过智能休眠模式在空闲时段切断偏置电路,可将静态电流降至微安级。但在高温环境下,漏电流会呈指数增长,成为不可忽视的损耗来源。

2. 动态功耗(Dynamic Power)——主导因素这是驱动功率的绝对大头,发生在MOS管开关过程中。驱动芯片需为栅极电容(Ciss)充放电,功耗与开关频率和栅极电荷成正比:

核心计算公式:

P_drive = Qg × Vgs × f_sw

其中Qg为总栅极电荷(单位nC),Vgs为驱动电压摆幅(单位V),f_sw为开关频率(单位Hz)。

该公式的物理意义是:每次开关消耗Qg×Vgs焦耳能量,每秒开关f_sw次,故功率为两者乘积。例如Qg=50nC、Vgs=12V、f_sw=500kHz时,驱动功率为0.3W。

3. 导通损耗(Conduction Loss)驱动芯片内部的推挽输出级存在导通电阻RDS(on),电流通过时产生焦耳热。这部分损耗与驱动电流的平方成正比,在连续输出时较为显著。

二、关键影响因素分析

1. 开关频率(f_sw)开关频率每提高一倍,驱动功率线性增加一倍。这是高频电源(>500kHz)中驱动芯片发热的主要原因。设计时应在满足响应速度的前提下,尽量选择最低的有效开关频率。

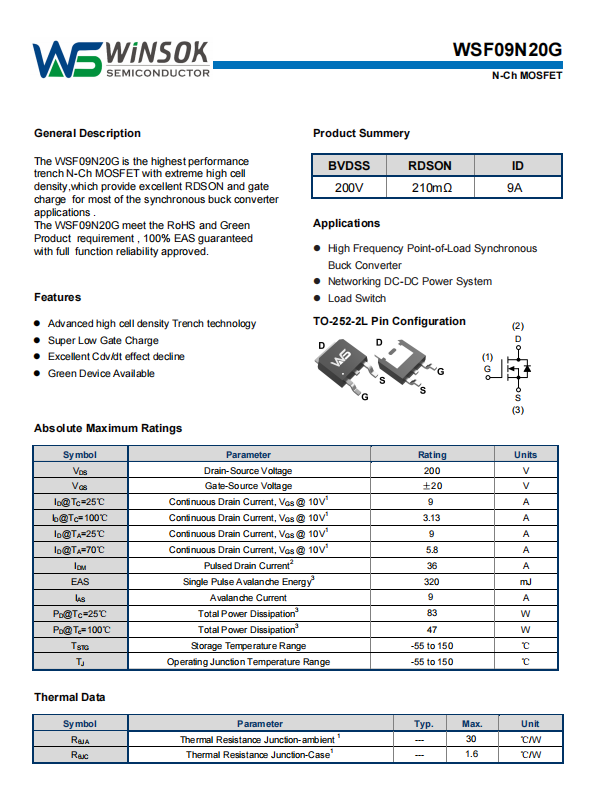

2. 栅极电荷(Qg)Qg由栅源电荷Qgs、栅漏电荷Qgd和过驱动电荷Qod组成,直接决定开关能量。选择低Qg的MOSFET(如SiC、GaN器件)可显著降低驱动功耗。例如,SiC MOSFET的Qg仅为硅器件的1/5,驱动功率相应降低80%。

3. 驱动电压(Vgs)驱动电压摆幅越大,每次开关消耗的能量越多。但Vgs过低会导致MOS导通不充分,RDS(on)增大,得不偿失。通常需权衡:低压MOS(<100V)可用5V驱动,高压MOS(>100V)需10-15V驱动。

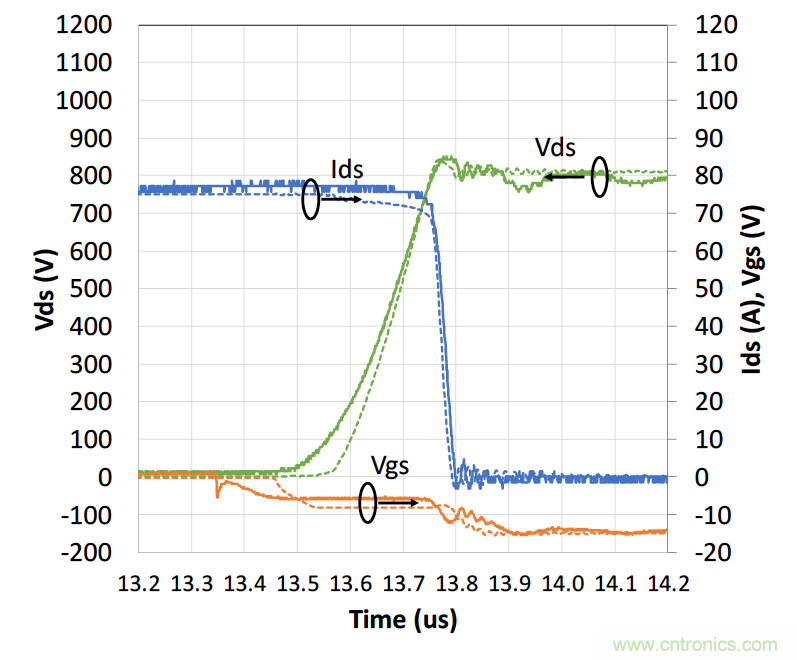

4. 栅极电阻(Rg)Rg影响开关速度和损耗。阻值过小,开关过快,di/dt过大导致EMI和电压尖峰;阻值过大,开关慢,交越导通损耗增加。最佳Rg值通过实验确定,使开关损耗与EMI达到平衡。

5. 负载特性容性负载在开关瞬间需吸收大电流,驱动芯片需提供额外电荷,功耗增加。感性负载导致电压尖峰,需更强的驱动能力抑制米勒效应。

三、驱动功率的工程计算

计算公式体系:

平均驱动电流(用于功耗估算):

I_avg = Qg × f_sw

实例:Qg=50nC,f_sw=1MHz时,I_avg=50mA

峰值驱动电流(决定开关速度):

I_peak = Qg / t_rise

实例:Qg=60nC,要求上升时间30ns,需I_peak=2A

总驱动功率(完整表达式):

P_total = P_static + P_dynamic + P_cond = I_leakage × Vcc + Qg × Vgs × f_sw + I_rms² × Rds(on)

实例计算: 假设驱动芯片为TC4420,驱动IRF540N(Qg=60nC),Vgs=12V,f_sw=100kHz,tr=50ns:

I_avg = 60nC × 100kHz = 6mA

I_peak = 60nC / 50ns = 1.2A

P_dynamic = 60nC × 12V × 100kHz = 0.072W

TC4420静态电流1.5mA@5V,P_static = 7.5mW

总功耗约0.08W,远小于芯片额定0.5W

四、优化策略与工程实践

1. 选择合适的驱动电压

低压MOS(<100V)采用3.3V或5V驱动,降低动态功耗

高压MOS(>100V)选择10-15V驱动,平衡RDS(on)和驱动损耗

自适应电压调节技术根据负载动态调整Vgs

2. 优化栅极电阻Rg通过实验或仿真确定最佳Rg值。例如,采用自适应栅极驱动技术,在开通时用较小Rg加速,关断时用较大Rg抑制振铃。分级驱动(Multi-Stage Driving)先以低电压预充电,再快速切换至高电压,减少开关损耗。

3. 采用低Qg的MOS管选择SiC(碳化硅)或GaN(氮化镓)MOSFET,其Qg仅为硅器件的1/5至1/10,驱动功率大幅降低。例如,GaN器件Qg=5nC,驱动功率比硅器件降低80%。

4. 谐振驱动技术利用LC谐振回收栅极能量,显著降低动态功耗。在MHz级高频应用中,谐振驱动可将驱动功率减少50%以上。

5. 优化PCB布局

缩短驱动回路长度<10mm,降低寄生电感

使用低ESR/ESL电容,减少开关振铃

驱动芯片靠近MOS管放置,减小传输延迟

五、实际案例分析

案例1:45W快充(NCE6050A)

Qg=50nC,f_sw=900kHz,目标tr=30ns

I_peak = 50nC / 30ns = 1.67A,取2A峰值

P_dynamic = 50nC × 12V × 900kHz = 0.54W

选型驱动芯片峰值能力≥3A(如UCC27511)

驱动功耗0.54W,需确保芯片结温<100℃

案例2:电机驱动系统优化

原设计f_sw=100kHz,Qg=80nC,P_drive=0.96W

优化策略:频率降至20kHz,Qg降至40nC

新功耗P_drive=40nC×12V×20kHz=0.096W,降低90%

同时采用自适应死区控制,避免上下管直通,降低交越损耗

六、工程实践要点

驱动芯片选型:确保峰值电流>1.5×I_peak,平均功耗<0.5×P_max(考虑温度降额)

温度降额:驱动芯片允许功耗随环温升高而降低,需在85℃下核算功耗

米勒平台影响:Qg中的Qgd(米勒电荷)在开关过程中造成电流尖峰,驱动芯片需具备瞬时>3A的灌电流能力

负压关断:增加-2V至-5V负压可加速关断,但会略微增加驱动功率(ΔVgs增大)

测试验证:通过热成像仪监测驱动芯片壳温,确保满载下<80℃

核心结论:MOS驱动功率的计算需采用P_drive = Qg × Vgs × f_sw这一动态功耗主导公式,而非简单的P=V×I。优化关键在于降低Qg、合理选择f_sw和Vgs、采用智能驱动架构,并通过实验验证芯片温升,避免驱动芯片成为系统瓶颈。