芯片为什么难造摩尔定律到瓶颈了吗

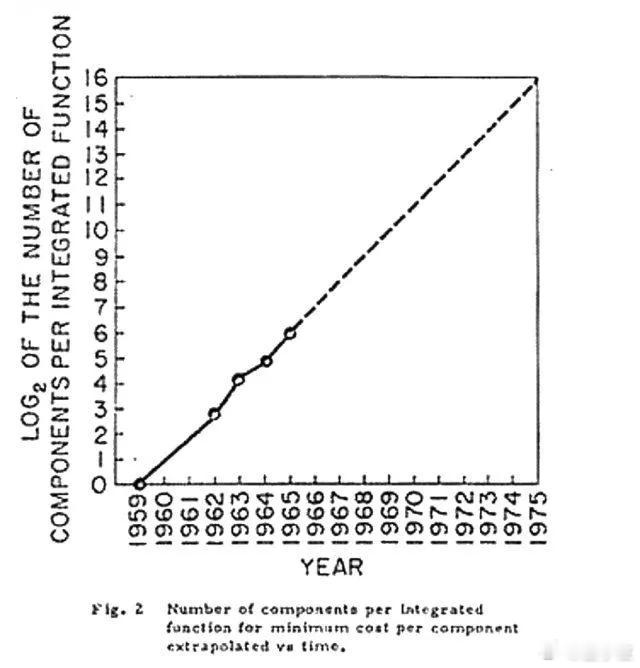

过去几十年,芯片性能的爆炸式增长靠的是摩尔定律,即每两年,晶体管密度就会翻倍。但摩尔定律,似乎达到了瓶颈。

网友Charles Rosenbauer文章写道,现在的问题不在于技术“还能不能做”,而在于“谁负担得起”。芯片制造的天花板,不是物理限制,而是经济限制。

25年前,全球能自己造先进芯片的公司有40多家,建个晶圆厂要20–40亿美元;如今剩下的只剩2–3家,建厂成本突破1000亿美元。照这趋势推算,10年后,全球没有任何一家公司能负担得起建厂费用。

一、规格不统一,或存虚标

过去,“nm”代表的是晶体管栅极宽度,但现在用的是FinFET结构,而所谓“多少nm工艺”,已经不是实际的晶体管尺寸了。

这不禁让人怀疑,为了让进展看起来“有在继续”,厂商开始发明新单位,比如Intel的20A、14A(1A=0.1nm),实则没有统一标准,变成一种市场宣传语言。

再看先进制程的密度,其实早就触碰到空间限制:

- 单个晶体管实际占地60nm×60nm;

- 即便用13.5nm波长的EUV光刻技术,图案分辨率也到瓶颈;

- ASML目前推进的High-NA EUV,只能将精度略微提升到6–7nm级别,但制造难度与设备成本急剧上升,一台设备已达1.5亿美元。

二、结构太复杂,让人劝退

传统平面晶体管早在15年前就被淘汰,如今的主力FinFET,再往前走是GAAFET(全包围栅极),Intel称其为RibbonFET。下一代是CFET,把不同类型的晶体管上下叠放,实现真正的三维结构。

听上去前沿,但每一步的制造复杂度都在指数级上涨,缺陷率也同步飙升,导致生产成本无法控制。正因如此,像GlobalFoundries这样的巨头已退出先进工艺竞赛,只做成熟制程。

三、成本暴涨,小厂活不下去

另一个已经威胁到生态的是光罩成本。从28nm节点开始,每套光罩从百万级涨到千万级,到3nm已突破4000万美元。对于量产百万级的厂商来说,光罩成本还能摊一摊;而中小客户只能望而却步。

这冲击了TSMC这样的代工巨头,因为它的商业模式建立在服务大量中小客户的基础上。先进节点越卷,小客户就越买不起,最终可能形成只有苹果、英伟达、谷歌这类大客户能定制高端芯片的局面。

四、有人开始寻找Plan B

Intel押注的“背面供电”技术,本质上是把供电线路从芯片背部引入,从而减少正面布线干扰,提高性能。但这是个一次性优化,不能像过去那样重复叠加,属于“榨干最后一点潜力”的操作。

与此同时,也有声音开始探索降低制造门槛,比如用更高缺陷容忍度的架构(参考内存芯片),换取低成本的芯片制造;又比如让光刻设备重回“简约”路线,用新型X射线系统替代复杂EUV。甚至有极客在车库里自己造出90年代水平的芯片,足以跑现代操作系统。

如果未来芯片性能提升放缓,那“买一颗好芯片用十年”的模式或成现实。芯片行业也许会像汽车市场那样——真正的增量来自“二手市场”和“再利用”。

五、说回摩尔定律

Gordon Moore当年就说过,这个“定律”本质上是经济规律,而不是物理规律。如今我们看到的是,它的经济基础正在崩塌:每一代技术迭代,设备更贵、步骤更多、客户更少、失败代价更高。整个产业开始进入一个结构性困境:

- 你必须做得更复杂,但复杂意味着更贵;

- 你想服务更多客户,但客户反而被价格挡在门外;

- 你还想继续卷制程,但没有人再愿意为此买单。

作者最后总结道,如果说过去几十年,芯片奇迹靠全球供应链协同“堆”出来,那么接下来的十年,就是重新找回“简单”的过程。(配图由AI生成)

原文链接:bzolang.blog/p/the-unsustainability-of-moores-law